Семейства видеокарт AMD(ATI) RADEON Справочная информация (original) (raw)

Справочная информация о семействе видеокарт Radeon X

Справочная информация о семействе видеокарт Radeon X1000

Справочная информация о семействе видеокарт Radeon HD 2000

Справочная информация о семействе видеокарт Radeon HD 4000

Справочная информация о семействе видеокарт Radeon HD 5000

Справочная информация о семействе видеокарт Radeon HD 6000

Справочная информация о семействе видеокарт Radeon HD 7000

Справочная информация о семействе видеокарт Radeon 200

Справочная информация о семействе видеокарт Radeon 300

Спецификации чипов семейства R[V]4XX и некоторых из RV3XX

| кодовое имя | R481 | R480 | R430 | R423 | R420 | RV410 | RV380 | RV370 |

|---|---|---|---|---|---|---|---|---|

| базовая статья | здесь | здесь | здесь | |||||

| технология (нм) | 130 | 110 | 130 | 110 | 130 | 110 | ||

| транзисторов (М) | 160 | 120 | 75 | |||||

| пиксельных процессоров | 16 | 8 | 4 | |||||

| текстурных блоков | 16 | 8 | 4 | |||||

| блоков блендинга | 16 | 8 | 4 | |||||

| вершинных процессоров | 6 | 2 | ||||||

| шина памяти | 256 (64х4) | 128 (64х2) | ||||||

| типы памяти | DDR, DDR2, GDDR3 | DDR, DDR2 | ||||||

| системная шина чипа | AGP 8x | PEG 16х | AGP 8x | PEG 16х | PEG 16х | |||

| RAMDAC | 2 х 400МГц | |||||||

| интерфейсы | TV-Out TV-In (нужен чип захвата) 2 x DVI (нужны внешние интерфейсные чипы) | |||||||

| вершинные шейдеры | 2.0 | |||||||

| пиксельные шейдеры | 2.0b | 2.0 | ||||||

| точность пиксельных вычислений | FP24 | |||||||

| точность вершинных вычислений | FP32 | |||||||

| форматы компонент текстур | FP32, FP16 (без фильтрации) I8 DXTC*, S3TC 3Dc | |||||||

| форматы рендеринга | FP32 и FP16 (без блендинга и MSAA) I8 | |||||||

| MRT | есть | |||||||

| Aнтиалиасинг | 2х, 4x и 6х MSAA псевдослучайное расположение отсчетов на решетке 12х12 | |||||||

| генерация Z | 1х в режиме без цвета, 2х в режиме MSAA | |||||||

| буфер шаблонов | двусторонний | обычный | ||||||

| технологии теней | специальные технологии отсутствуют |

Спецификации референсных карт на базе чипов семейств R[V]4XX и RV3XX

| карта | чипшина | блоков PS/TMU/VS | частота ядра (МГц) | частота памяти (МГц) | объем памяти (Мбайт) | ПСП (Гбайт)бит | тексель рэйт (Мтекс) | филлрэйт (Мпикс) |

|---|---|---|---|---|---|---|---|---|

| RADEON X800 PRO | R420 AGP | 12/12/6 | 475 | 450(900) | 256 GDDR3 | 28.8 (256) | 6400 | |

| RADEON X800 XT PE | R420 AGP | 16/16/6 | 520 | 560(1120) | 256 GDDR3 | 35.8 (256) | 8320 | |

| RADEON X300 | RV370 PEG16х | 4/4/2 | 325 | 200(400) | 128 DDR | 6.4 (128) | 1300 | |

| RADEON X300 SE | RV370 PEG16х | 4/4/2 | 325 | 200(400) | 128 DDR | 3.2 (64) | 1300 | |

| RADEON X600 PRO | RV380 PEG16х | 4/4/2 | 400 | 300(600) | 128 DDR | 9.6 (128) | 1600 | |

| RADEON X600 XT | RV380 PEG16х | 4/4/2 | 500 | 370(740) | 128 DDR | 11.8 (128) | 2000 | |

| RADEON X800 XT | R420 AGP | 16/16/6 | 500 | 500(1000) | 256 GDDR3 | 32.0 (256) | 8000 | |

| RADEON X800 XT | R423 PEG16х | 16/16/6 | 500 | 500(1000) | 256 GDDR3 | 32.0 (256) | 8000 | |

| RADEON X700 [LE] | RV410 PEG16х | 8/8/6 | 400 | 350(700) | 128 GDDR3 | 11.2 (128) | 3200 | |

| RADEON X700 PRO | RV410 PEG16х | 8/8/6 | 425 | 430(860) | 256 GDDR3 | 13.8 (128) | 3400 | |

| RADEON X700 XT | RV410 PEG16х | 8/8/6 | 475 | 525(1050) | 128 GDDR3 | 16.8 (128) | 3800 | |

| RADEON X800 SE | R420 AGP | 8/8/6 | 425 | 400(800) | 256 GDDR3 | 25.6 (256) | 3400 | |

| RADEON X800 | R430 PEG16х | 12/12/6 | 400 | 350(700) | 256 GDDR3 | 22.4 (256) | 4800 | |

| RADEON X800 XL | R430 PEG16х | 16/16/6 | 400 | 500(1000) | 256 GDDR3 | 32.0 (256) | 6400 | |

| RADEON X850 PRO | R480 PEG16х | 12/12/6 | 507 | 520(1040) | 256 GDDR3 | 33.3 (256) | 6804 | |

| RADEON X850 XT | R480 PEG16х | 16/16/6 | 520 | 540(1080) | 256 GDDR3 | 34.6 (256) | 8320 | |

| RADEON X850 XT PE | R480 PEG16х | 16/16/6 | 540 | 590(1180) | 256 GDDR3 | 37.8 (256) | 8640 | |

| RADEON X700 LE | RV410 AGP | 8/8/6 | 400 | 350(700) | 128 GDDR3 | 11.2 (128) | 3200 | |

| RADEON X700 PRO | RV410 AGP | 8/8/6 | 425 | 430(860) | 256 GDDR3 | 13.8 (128) | 3400 | |

| RADEON X800 | R430 AGP | 12/12/6 | 400 | 350(700) | 256 GDDR3 | 22.4 (256) | 4800 | |

| RADEON X800 XL | R430 AGP | 16/16/6 | 400 | 500(1000) | 256 GDDR3 | 32.0 (256) | 6400 | |

| RADEON X850 PRO | R481 AGP | 12/12/6 | 507 | 520(1040) | 256 GDDR3 | 33.3 (256) | 6804 | |

| RADEON X850 XT | R481 AGP | 16/16/6 | 520 | 540(1080) | 256 GDDR3 | 34.6 (256) | 8320 | |

| RADEON X850 XT PE | R481 AGP | 16/16/6 | 540 | 590(1180) | 256 GDDR3 | 37.8 (256) | 8640 | |

| RADEON X300 SE 128 (HM) | RV370 PEG16х | 4/4/2 | 325 | 300(600) | 32 DDR | 4.8 (64) | 1300 | |

| RADEON X300 SE 256 (HM) | RV370 PEG16х | 4/4/2 | 325 | 300(600) | 128 DDR | 4.8 (64) | 1300 | |

| RADEON X740 XL | RV410 PEG16х | 8/8/6 | 425 | 450(900) | 128 GDDR3 | 14.4 (128) | 3400 | |

| RADEON X700 SE | RV410 AGP | 4/4/6 | 400 | 250(500) | 128 GDDR3 | 4.0 (64) | 1600 | |

| RADEON X550 | RV370 PEG16х | 4/4/2 | 400 | 250(500) | 128 DDR | 8.0 (128) | 1600 | |

| RADEON X800 XL | R430 PEG16х | 16/16/6 | 400 | 500(1000) | 512 GDDR3 | 32.0 (256) | 6400 | |

| RADEON X850 XT CFE | R480 PEG16х | 16/16/6 | 520 | 540(1080) | 256 GDDR3 | 34.6 (256) | 8320 | |

| RADEON X800 CFE | R430 PEG16х | 16/16/6 | 400 | 500(1000) | 128/256 GDDR3 | 32.0 (256) | 6400 | |

| карта | чип шина | блоков PS/TMU/VS | частота ядра (МГц) | частота памяти (МГц) | объем памяти (Мбайт) | ПСП (Гбайт) бит | тексель рэйт (Мтекс) | филл рэйт (Мпикс) |

Подробности: R420, серия RADEON X800

Спецификации R420

- Кодовое имя чипа R420

- Технология 130 нм (TMSC, low-k, медные соединения)

- 160 миллионов транзисторов

- FС корпус (перевернутый чип, без металлической крышки)

- 256 бит интерфейс памяти

- До 512 мегабайт DDR/DDR2/GDDR3 памяти

- AGP 8x шинный интерфейс (также есть PCI-Express версия чипа - R423)

- 16 Пиксельных процессоров, по одному текстурному блоку на каждом

- 6 Вершинных процессоров

- Вычисление, блендинг и запись до 16 полных (цвет, глубина, буфер шаблонов) пикселей за такт

- Вычисление и запись до 32 значений глубины и буфера шаблонов за такт

- MSAA 2x/4x/6х, с гибко программируемыми паттернами отсчетов. Сжатие буфера кадра и буфера глубины в MSAA режимах. Возможность менять MSAA паттерны от кадра к кадру (Temporal AA)

- Анизотропная фильтрация степени до 16х включительно

- Все необходимое для поддержки пиксельных и вершинных шейдеров версии 2.0

- Дополнительные возможности пиксельных шейдеров на основе расширенной версии 2.0 - 2.0.b

- Дополнительные возможности вершинных шейдеров, сверх базовых 2.0

- Новая техника сжатия текстур, оптимизированная для сжатия двухкомпонентных карт нормалей (т.н. 3Dc, степень сжатия 4:1)

- Поддерживается рендеринг в буфера плавающего формата, с точностью FP16 и FP32 на компоненту, возможность блендинга отсутствует

- Поддерживаются трехмерные и FP (плавающие) форматы текстур, без текстурной фильтрации

- Поддержка «двустороннего» буфера шаблонов

- MRT (Multiple Render Targets — рендеринг в несколько буферов)

- 2 x RAMDAC 400 МГц

- 2 x DVI интерфейса

- TV-Out и TV-In интерфейс (требуются интерфейсные чипы)

- Возможность программируемой обработки видео - пиксельные процессоры задействуются для обработки видео потока (задачи компрессии, декомпрессии и постобработки)

- 2D ускоритель с поддержкой всех функций GDI+

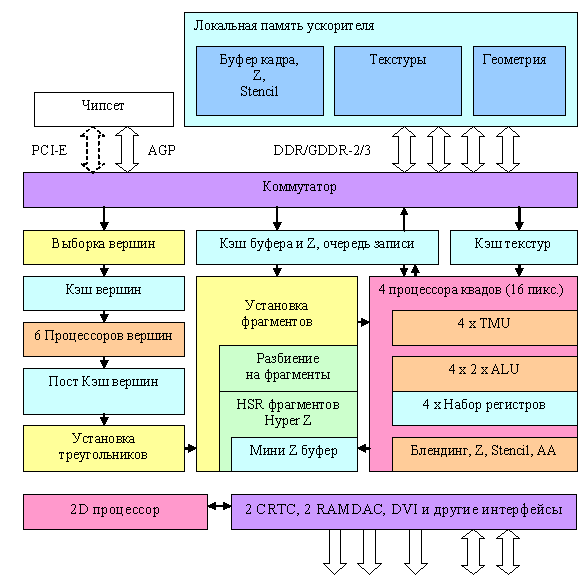

Общая схема чипа R420

Пытливый читатель сразу отметит, что схема практически совпадает с NV40. Ничего удивительного - обе фирмы стараются создать оптимальное решение и уже несколько поколений исповедуют проверенную и эффективную организацию общей структуры графического конвейера. Существенные отличия кроются внутри блоков и в первую очередь - в пиксельных и вершинных процессорах.

Как и у NV40, в наличии шесть вершинных процессоров и четыре независимых пиксельных процессора, каждый из которых работает с одним квадом (фрагментом 2х2 пикселя). Скорее всего, в отличие от NV40, присутствует только один уровень кэширования данных текстур. В наличии четыре независимых процессора квадов, каждый из которых может быть отключен - таким образом, в зависимости от потребностей рынка и наличия бракованных чипов можно отключать один, два или даже три процессора, производя, таким образом карты, обрабатывающие 4, 8, 12 или 16 пикселей за такт.

А теперь, по традиции увеличим степень детализации в самых интересных местах:

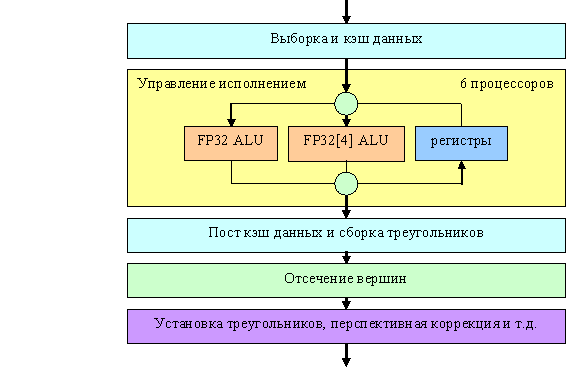

Вершинные процессоры и выборка данных

Приведем блок схему вершинного процессора R420:

Сам процессор на схеме обозначен желтым прямоугольником, остальные окружающие его блоки показаны для более полной картины. Заявлено, что R420 содержит 6 независимых процессоров (мысленно скопируем желтый блок шесть раз). Вершинные блоки не соответствуют ни полной спецификации vs 3.0 (отсутствует возможность доступа к текстурам и динамические ветвления) ни расширенной спецификации 2.0 в понимании NVIDIA (т.н. версии 2.0.а, которая предполагает поддержку предикатов и динамических переходов). Что касается арифметической производительности, то за один такт вершинный процессор R420 может выполнить одну векторную операцию (до 4-х компонент FP32) и одну скалярную FP32 операцию одновременно, так же как и вершинный процессор NV40.

Напомним, как выглядит сводная табличка параметров вершинных процессоров современных ускорителей с точки зрения вершинных шейдеров DirectX 9 API:

| Версия вершинных шейдеров | 2.0 (R3XX, R42X) | 2.a (NV3X) | 3.0 (NV4X, G7X, R5XX) |

|---|---|---|---|

| Число инструкций в коде шейдера | 256 | 256 | 512 и более |

| Число исполняемых инструкций | 65535 | 65535 | 65535 и более |

| Предикаты | Нет | Есть | Есть |

| Временных регистров | 12 | 13 | 32 |

| Константных регистров | 256 и более | 256 и более | 256 и более |

| Статические переходы | Да | Да | Да |

| Динамические переходы | Нет | Да | Да |

| Глубина вложенности динамических переходов | Нет | 24 | 24 |

| Выбор значений текстур | Нет | Нет | Да (4) |

Еще один интересный аспект, который исследуется в практических статьях - производительность эмуляции FFP (T&L). Напомним, что R3XX во многом проигрывал чипам NVIDIA из-за отсутствия специальных аппаратных блоков расчета освещения, ускорявших эмуляцию T&L вот уже в трех поколениях чипов NVIDIA.

Пиксельные процессоры и организация закраски

Рассмотрим пиксельную архитектуру R420 в порядке следования данных. Итак, после установки параметров треугольника нас ждет:

Остановимся на самых интересных фактах. Во-первых, если ранее в R3XX было максимум два процессора квадов, обрабатывающих за такт блок из четырех пикселей (2х2) то теперь таких процессоров стало четыре. Они полностью независимы и каждый из них может исключаться из работы (например, для создания облегченной версии чипа с тремя процессорами при наличии брака в одном из них).

Отметим, что во многом схема похожа на NV40, но есть и кардинальные отличия, на которых мы остановимся подробнее. Итак, сначала треугольник разбивается на блоки первого уровня (8х8 или 4х4 в зависимости от разрешения рендеринга) и происходит первая ступень отбрасывания невидимых блоков, на основе данных полностью размещенного на чипе мини Z буфера. Его объем не афишируется, но, судя по всему, в R420 он занимает несколько менее 200 килобайт. Всего на этой стадии может быть откинуто до 4 блоков за такт, т.е. до 256 невидимых пикселей.

Затем происходит вторая ступень разбиения - на сей раз, на квады размером 2х2 и происходит раннее отсечение полностью невидимых квадов, на основе хранимого в видео памяти Z буфера второго уровня, с гранулярностью покрытия 2х2. Отметим, что в зависимости от режима MSAA один элемент этого буфера может соответствовать 4 (нет), 8(MSAA 2х), 16 (MSAA 4х) или даже 24 (6х MSAA) точкам в буфере кадра, вот почему его выделили в отдельную структуру, занимающую промежуточный уровень между мини буфером глубины полностью расположенном на чипе и окончательным буфером глубины базового уровня. Таким образом, в продуктах NVIDIA мы имеем дело с двухуровневой организацией HSR и буфера глубины, а в продуктах ATI - с трехуровневой.

Затем происходит установка квадов, и их распределение по активным пиксельным процессорам. А вот еще дальше начинаются самые существенные отличия R420 от NV40:

Алгоритм работы пиксельного процессора NVIDIA: Цикл по командам шейдера

- Считать микрокод следующей команды

- Сконфигурировать текстурный модуль и все ALU

- Цикл по всем квадам в очереди

* Прогнать квад через процессор, TMU и ALU - Конец цикла по квадам

Конец цикла по командам шейдера

Алгоритм работы пиксельного процессора ATI

Цикл по 4 фазам

- Цикл по все квадам в очереди

* Цикл по выбираемым текстурам в этой фазе (до 8)

* Выбрать значение текстуры

* Конец цикла по текстурам - Цикл по вычислительным командам в этой фазе (до 128)

* Выполнить команду - Конец цикла

- Конец цикла по квадам

Конец цикла по 4 фазам.

Итак, NVIDIA постепенно исполняет команды (а точнее суперскалярные пачки команд, включая команды выборки текстур), прогоняя через каждую команду все квады находящиеся в обработке. ATI же разбивает шейдер на четыре фазы (вот откуда ограничение на глубину зависимых выборок не более 4), в каждой из которых сначала осуществляется выборка всех данных текстур необходимых для этой фазы, а затем уже все вычисления над полученными данными. В том числе, и вычисление новых координат, для выборки текстур в следующей фазе.

Какой подход лучше? Сказать однозначно нельзя. Подход ATI хуже приспособлен к сложным шейдерам с управлением потоком команд или многочисленными зависимыми выборками. С другой стороны, вычисления внутри каждой из четырех фаз происходят по похожей на CPU схеме - выполняются все команды, команда за командой, для одного квада, затем берется следующий квад и т.д. Таким образом, во время вычислений можно использовать полноценный пул из временных регистров, без какой либо потери производительности и пенальти за использование более 4 регистров, которое мы имеем в NV40. Кроме того, подход ATI требует менее длинных по числу стадий конвейеров. Следовательно, расходуется меньше транзисторов и потенциально достигаются более высокие тактовые частоты (или, что одно и то же, более высокий выход годных чипов на фиксированной частоте). Хорошо предсказуема производительность того или иного шейдера, легче писать их код, когда не надо заботиться о равномерной группировке текстурных и вычислительных команд или расходе временных регистров.

Из недостатков - многочисленные ограничения. Ограничение на число зависимых выборок, ограничение на число команд в одной фазе, необходимость хранить весь микрокод шейдера для четырех фаз «под рукой», т.е. прямо в пиксельном процессоре. Существует возможность задержек в случае интенсивных зависимых выборок текстур, следующих друг за другом (это сглаживается наличием набора одновременно обрабатываемых квадов, но их число не столь велико, как у NVIDIA).

Фактически, подход ATI оптимален для реализации шейдеров 2.0, без динамического контроля исполнения и с серьезно ограниченной длиной кода. Любые попытки «прикрутить» к подобной архитектуре пиксельного процессора неограниченную длину шейдеров и тем более неограниченную гибкость в текстурных выборках неизбежно вызовут множество проблем.

На схеме пиксельного процессора обозначена логика F-буфера - механизма для записи и восстановления параметров временных переменных шейдера. Это ухищрение позволяет исполнять шейдеры, превышающие по длине или числу зависимых (да и обычных тоже) выборок текстур ограничения пиксельного процессора ценой дополнительных проходов, что само по себе не является бесплатным решением и далеко от идеала. По мере роста сложности шейдера число проходов и сохраняемых временно в видеопамяти данных будет возрастать, а вместе с ними будет возрастать и штраф по сравнению с архитектурами, подобными тем, что мы видим у NVIDIA, которые не ограничены длиной или сложностью шейдера.

Впрочем, вернемся к особенностям архитектуры пиксельных процессоров R420. Формат данных в процессорах при вычислениях - FP24, но операции с текстурными координатами при выборке текстур в TMU проводятся с большей точностью. Тут все как и в R3XX, на каждый пиксель приходится по два ALU, причем каждый из них может выполнить две различные операции по схеме 3+1 (как и в R3XX, но там ALU был один). Подробнее об этом написано в статье DX Current. Не поддерживается произвольное маскирование и перестановка компонент после операции, все только в рамках шейдеров 2.0 и чуть более длинных 2.0.b.

Таким образом, в зависимости от кода шейдера может быть выполнено от одной до четырех различных FP24 операций за такт, над векторами (размерность до 3) и скалярами и осуществлен один доступ к уже выбранным из текстуры в данной фазе данным. Производительность такой связки напрямую зависит от компилятора и кода, но очевидно, что мы имеем

- Минимум: один доступ к выбранным данным текстуры за такт

- Минимум: две операции за такт без доступа к текстуре

- Максимум: четыре операции за такт без доступа к текстуре

- Максимум: четыре операции за такт с доступом к текстуре

Что в пиковом варианте превышает возможности NV40. Но не забываем, что реально это решение менее гибко (постоянная схема 3+1) с точки зрения совмещения команд в суперскалярные пачки при компиляции. По сравнению с R3XX вычислительная эффективность новых конвейеров выросла вдвое и вместе с двукратным увеличением их числа и приростом тактовой частоты мы получаем солидное превосходство по сравнению с предыдущим поколением.

Все новые усовершенствования, такие как увеличенная длина шейдеров и новые регистры, доступны в новой версии шейдеров 2.0.b. Рассмотрим сводную таблицу возможностей разных версий:

| Версия пиксельного шейдера | 2.0 (R3XX) | 2.a (NV3X) | 2.b (R4XX) | 3.0 (NV4X/G7X, R5XX) |

|---|---|---|---|---|

| Вложенность выборок текстур до | 4 | Без ограничений | 4 | Без ограничений |

| Выборок значений текстур до | 32 | Без ограничений | Без ограничений | Без ограничений |

| Длина кода шейдера | 32 + 64 | 512 | 512 | 512 и более |

| Исполняемых инструкций шейдера | 32 + 64 | 512 | 512 | 65535 и более |

| Интерполяторы | 2 + 8 | 2 + 8 | 2 + 8 | 10 |

| Предикаты | нет | да | нет | да |

| Временных регистров | 12 | 22 | 32 | 32 |

| Константных регистров | 32 | 32 | 32 | 224 |

| Произвольная перестановка компонент | нет | да | нет | да |

| Инструкции градиента (DDX/DDY) | нет | да | нет | да |

| Глубина вложенности динамических переходов | нет | нет | нет | 24 |

Вернемся к схеме пиксельных процессоров и обратим внимание на ее нижнюю часть. Там расположены блоки, отвечающие за сравнение и модификацию значений цвета, прозрачности, глубины и буфера шаблонов, а также MSAA. В отличие от NV40, поддерживающей генерацию до 4х MSAA отсчетов на основе одного пикселя, R420 генерирует до 6. Причем, производительность расчета Z и буфера шаблонов, как и у NV40, удвоена относительно базовой скорости закраски - 32 значения в такт. Соответственно, 2х MSAA дается без пенальти по скорости, а 4х и 6х занимают 2 и 3 такта. Впрочем, в случае использования пиксельных шейдеров длиной хотя бы в несколько команд, это перестает быть заметным ограничением и не играет особой роли. Пропускная способность памяти становится более важной. Разумеется, в MSAA режимах сжимаются как данные о цвете, так и о глубине, и в оптимальном случае коэффициент сжатия приближается к числу MSAA сэмплов, т.е. в режиме MSAA 6х достигает 6:1.

В отличие от NV40, использующей RGMS (повернутую сетку отсчетов), R420, как и все чипы семейства R3XX, поддерживает псевдостохастические паттерны MSAA на базовой сетке 8х8. В итоге, качество сглаживания краев и наклонных линий при максимальных уровнях объективно выше. В новых драйверах доступен т.е. Temporal AA - временной АА. Суть его в простом изменении паттернов от кадра к кадру. Таким образом, если картинка соседних кадров будет без заметного мерцания усредняться нашим глазом или инертным ЖК монитором, то мы получим некоторое улучшение качества сглаживания, словно мы использовали больше отчетов MSAA. Производительность при этом не падает, но и эффект может проявляться по разному, в зависимости от монитора и частоты смены кадров в приложении.

Технологические новшества R420

Два основных новшества R4XX по сравнению с R3XX, помимо увеличения числа временных регистров и длины шейдера в пиксельном процессоре, которые мы причисляем к эволюционному развитию:

- Новый алгоритм F-буфера, позволяющий не вычислять тот или иной проход разбитого на части пиксельного шейдера для тех пикселей, которые в этом не нуждаются. Способен заметно оптимизировать производительность пиксельных шейдеров с условиями и ветвлениями в OpenGL, исполняемых в несколько проходов с помощью F-буфера.

- Новый метод компрессии текстур 3Dc, специально предназначенный для сжатия двухкомпонентных карт нормалей. Традиционные методы компрессии текстур рассчитаны на обычные текстуры - сжатие с потерями учитывает особенности нашего зрения в восприятии изображений. Однако они не подходят для сжатия карт нормалей - по сути, таблиц векторов.

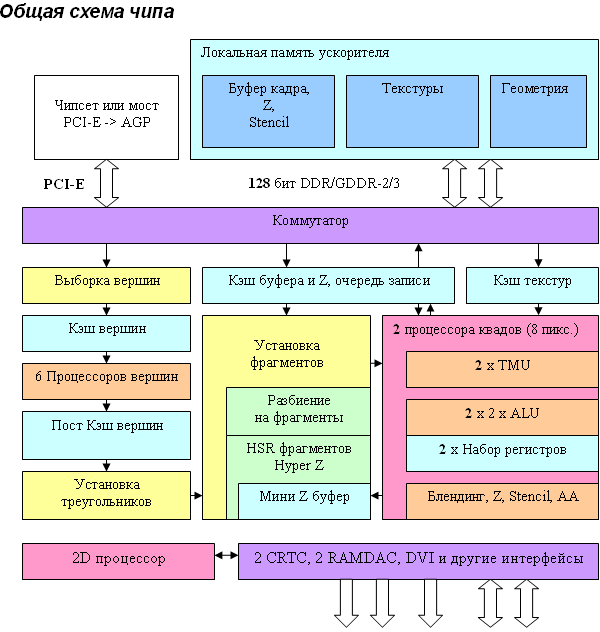

Подробности: RV410, серия RADEON X700

Спецификации RV410

- Кодовое имя чипа RV410

- Технология 110 нм (TMSC, low-k, медные соединения)

- 120 миллионов транзисторов

- FС корпус (перевернутый чип, без металлической крышки)

- 128 бит интерфейс памяти (двухканальный контроллер)

- До 256 мегабайт DDR/DDR2/GDDR3 памяти

- Встроенный PCI-Express x16 шинный интерфейс

- 8 Пиксельных процессоров, по одному текстурному блоку на каждом

- 6 Вершинных процессоров

- Вычисление, блендинг и запись до 8 полных (цвет, глубина, буфер шаблонов) пикселей за такт

- Вычисление и запись до 16 значений глубины и буфера шаблонов за такт

- MSAA 2x/4x/6х, с гибко программируемыми паттернами отсчетов. Сжатие буфера кадра и буфера глубины в MSAA режимах. Возможность менять MSAA паттерны от кадра к кадру (Temporal AA)

- Анизотропная фильтрация степени до 16х включительно

- Все необходимое для поддержки пиксельных и вершинных шейдеров версии 2.0

- Дополнительные возможности пиксельных шейдеров на основе расширенной версии 2.0 - 2.0.b

- Новая техника сжатия текстур, оптимизированная для сжатия двухкомпонентных карт нормалей (т.н. 3Dc, степень сжатия 4:1)

- Поддерживается рендеринг в буфера плавающего формата, с точностью FP16 и FP32 на компоненту, возможность блендинга отсутствует

- Поддерживаются трехмерные и FP (плавающие) форматы текстур, без текстурной фильтрации

- Поддержка «двустороннего» буфера шаблонов

- MRT (Multiple Render Targets — рендеринг в несколько буферов)

- 2 x RAMDAC 400 МГц

- 2 x DVI интерфейса

- TV-Out и TV-In интерфейс (для последнего требуется интерфейсный чип)

- Возможность программируемой обработки видео - пиксельные процессоры задействуются для обработки видео потока (задачи компрессии, декомпрессии и постобработки)

- 2D ускоритель с поддержкой всех функций GDI+

Спецификации референсной карты RADEON X700XT

- Частота ядра 475 МГц

- Эффективная частота памяти 1.05 ГГц (2*525 МГц)

- Шина памяти 128 бит

- Тип памяти GDDR3

- Объем памяти 128 или 256 мегабайт

- Пропускная способность памяти 16.8 гигабайт в сек.

- Теоретическая скорость закраски 3.8 гигапикселя в сек.

- Теоретическая скорость выборки текстур 3.8 гигатекселя в сек.

- Один VGA (D-Sub) и один DVI-I разъем

- TV-Out

- Потребляет менее 70 Ватт энергии (т.е. на PCI-Express карте разъем для дополнительного питания не нужен, рекомендован источник питания суммарной мощностью 300 или более Ватт)

Как видно, особые архитектурные отличия от R420 отсутствуют, что не удивительно - RV410 является масштабированным (путем уменьшения числа пиксельных процессоров и каналов контроллера памяти) решением, основанным на архитектуре R420. Ситуация такая же, как и у пары NV40/NV43, в этом поколении принципы построения архитектуры обоих конкурентов весьма схожи. Что же касается отличий RV410 и R420 - то они количественные (на схеме выделены жирным), а не качественные, с точки зрения архитектуры чип практически не изменился.

Итак, в наличии шесть (как и у R420, что может быть полезно для некоторых приложений, упирающихся в геометрическую производительность) вершинных процессоров, и два (у R420 их четыре) независимых пиксельных процессора, каждый из которых работает с одним квадом (фрагментом 2х2 пикселя). Как и в случае с NV43, PCI-Express является «родным» (реализованным на чипе) шинным интерфейсом, а AGP 8х платы содержат дополнительный мост PCI-E -> AGP (показан на схеме).

Архитектура вершинных и пиксельных процессоров, а также видеопроцессора осталась прежней - эти элементы детально описаны в обзоре RADEON X800 XT. А теперь поговорим о потенциальных тактических соображениях о том, что и почему было урезано. Вершинные и пиксельные процессоры RV410, судя по всему, остались неизменными, а вот внутренние кэши могли быть уменьшены, как минимум пропорционально числу конвейеров. Впрочем, число транзисторов не дает особых поводов для беспокойства - учитывая не столь большие размеры кэшей было бы разумнее оставить (так же как и в случае NV43, скомпенсировав тем самым заметную нехватку пропускной полосы памяти). Все технологии экономии ПСП были полностью сохранены - сжатие буфера глубины и буфера кадров, ранее отсечение с иерархическим буфером глубины и т.д.

Интересно, что в отличие от NV43, который может делать блендинг, записывая не более четырех результирующих пикселей за такт, пиксельные конвейеры RV410 полностью соответствуют R420 в этом плане. Соответственно, в случае простых шейдеров с одной текстурой RV410 должен получить почти двукратное преимущество в скорости закраски. В отличие от NVIDIA, имеющей крупный по транзисторам массив ALU, осуществляющих постобработку, проверку, генерацию Z и блендинг пикселей в плавающем формате, RV410 имеет более скромные комбинаторы и поэтому их число не было так урезано. Впрочем, в большинстве практических случаев уменьшенная полоса памяти все равно не позволит записать 3.8 полных гигапикселя в секунду.