hdlcoder.runWorkflow - Run HDL code generation and deployment workflow - MATLAB (original) (raw)

Run HDL code generation and deployment workflow

Syntax

Description

hdlcoder.runWorkflow([DUT](#bu0owlb-1-DUT)) runs the HDL code generation and deployment workflow with default workflow configuration settings.

hdlcoder.runWorkflow([DUT](#bu0owlb-1-DUT),[workflow_config](#bu0owlb-1-workflow%5Fconfig)) runs the HDL code generation and deployment workflow according to the specified workflow configuration, workflow_config.

A best practice is to use the HDL Workflow Advisor to configure the workflow, then export a workflow script. The commands in the workflow script create and configure a workflow configuration object that matches the settings in the HDL Workflow Advisor. The script includes the hdlcoder.runWorkflow command. To learn more, see Run HDL Workflow with a Script.

hdlcoder.runWorkflow([DUT](#bu0owlb-1-DUT),[workflow_config](#bu0owlb-1-workflow%5Fconfig), [Name,Value](#namevaluepairarguments)) runs the HDL code generation and deployment workflow according to the specified workflow configuration, workflow_config, with additional options specified by one or more Name,Value arguments.

A best practice is to use the HDL Workflow Advisor to configure the workflow, then export a workflow script. The commands in the workflow script create and configure a workflow configuration object that matches the settings in the HDL Workflow Advisor. The script includes the hdlcoder.runWorkflow command. To learn more, see Run HDL Workflow with a Script.

Examples

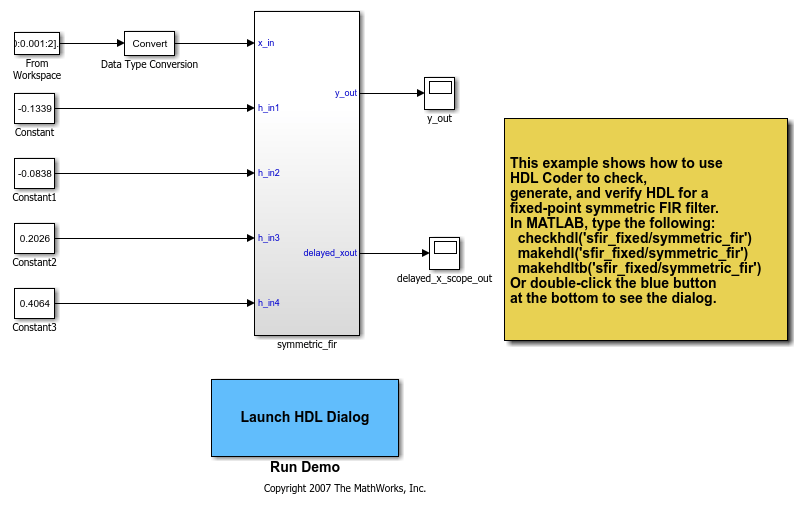

This example is a generic ASIC/FPGA workflow script that targets a Xilinx Virtex-7 device. It uses the Xilinx Vivado synthesis tool. The example generates HDL code for the sfir_fixed model, and performs FPGA synthesis and analysis.

Before running the Workflow

Before running the workflow, you must have the synthesis tool installed. Use hdlsetuptoolpath to specify the path to your synthesis tool.

hdlsetuptoolpath('ToolName','Xilinx Vivado','ToolPath',... 'L:\Xilinx\Vivado\2016.2\bin\vivado.bat');

Prepending following Xilinx Vivado path(s) to the system path: L:\Xilinx\Vivado\2016.2\bin

Specify the model for running the workflow

To run the HDL workflow with default settings for a DUT subsystem, modelname/DUT, at the command line, enter:

open_system('sfir_fixed');

Model HDL Parameters

Set Model HDL parameters

hdlset_param('sfir_fixed', 'SynthesisTool', 'Xilinx Vivado'); hdlset_param('sfir_fixed', 'SynthesisToolChipFamily', 'Virtex7'); hdlset_param('sfir_fixed', 'SynthesisToolDeviceName', 'xc7vx485t'); hdlset_param('sfir_fixed', 'SynthesisToolPackageName', 'ffg1761'); hdlset_param('sfir_fixed', 'SynthesisToolSpeedValue', '-2');

Workflow Configuration Settings

- Construct the Workflow Configuration Object with default settings

- Specify the path to your project folder. This step is optional

hWC = hdlcoder.WorkflowConfig('SynthesisTool','Xilinx Vivado', ... 'TargetWorkflow','Generic ASIC/FPGA');

hWC.ProjectFolder = 'C:/Temp/hdl_prj';

Run the workflow

hdlcoder.runWorkflow('sfir_fixed/symmetric_fir', hWC);

Workflow begin.

Loading settings from model.

++++++++++++++ Task Generate RTL Code and Testbench ++++++++++++++

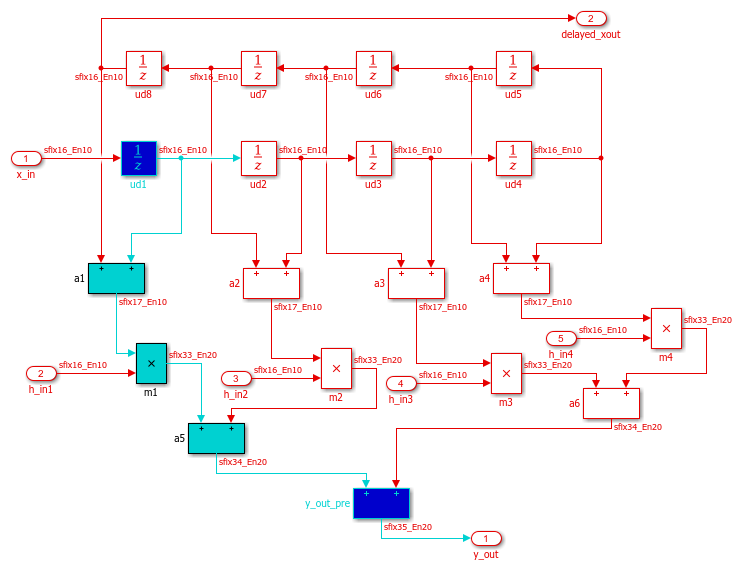

Generating HDL for 'sfir_fixed/symmetric_fir'.

Starting HDL check.

Begin VHDL Code Generation for 'sfir_fixed'.

Working on sfir_fixed/symmetric_fir as C:\Temp\hdl_prj\hdlsrc\sfir_fixed\symmetric_fir.vhd.

Creating HDL Code Generation Check Report file://C:\Temp\hdl_prj\hdlsrc\sfir_fixed\symmetric_fir_report.html

HDL check for 'sfir_fixed' complete with 0 errors, 0 warnings, and 0 messages.

HDL code generation complete.

++++++++++++++ Task Create Project ++++++++++++++

Generating Xilinx Vivado 2016.2 project: C:\Temp\hdl_prj\vivado_prj\symmetric_fir_vivado.xpr

Generated logfile: C:\Temp\hdl_prj\hdlsrc\sfir_fixed\workflow_task_CreateProject.log

Task "Create Project" successful.

++++++++++++++ Task Run Synthesis ++++++++++++++

Generated logfile: C:\Temp\hdl_prj\hdlsrc\sfir_fixed\workflow_task_RunSynthesis.log

Task "Run Synthesis" successful.

++++++++++++++ Task Annotate Model with Synthesis Result ++++++++++++++

Parsing the timing file...

Matched Source = 'sfir_fixed/symmetric_fir/ud1_out1'

Matched Destination = 'sfir_fixed/symmetric_fir/y_out'

Highlighting CP 1 from 'sfir_fixed/symmetric_fir/ud1_out1' to 'sfir_fixed/symmetric_fir/y_out' ...

Click here to reset highlighting.

Workflow complete.

Input Arguments

Full path to the DUT, specified as a character vector.

Example: 'hdlcoder_led_blinking/led_counter'

HDL code generation and deployment workflow configuration, specified as an hdlcoder.WorkflowConfig object.

Name-Value Arguments

Specify optional pairs of arguments asName1=Value1,...,NameN=ValueN, where Name is the argument name and Value is the corresponding value. Name-value arguments must appear after other arguments, but the order of the pairs does not matter.

Before R2021a, use commas to separate each name and value, and enclose Name in quotes.

Example: 'Verbosity','on'

When Verbosity is left to default value of'off', minimal code generation progress messages are displayed as the code generation and deployment workflow runs. WhenVerbosity is set to 'on', more detailed progress messages are displayed.

Version History

Introduced in R2015b