IP Caching for Faster Reference Design Synthesis - MATLAB & Simulink (original) (raw)

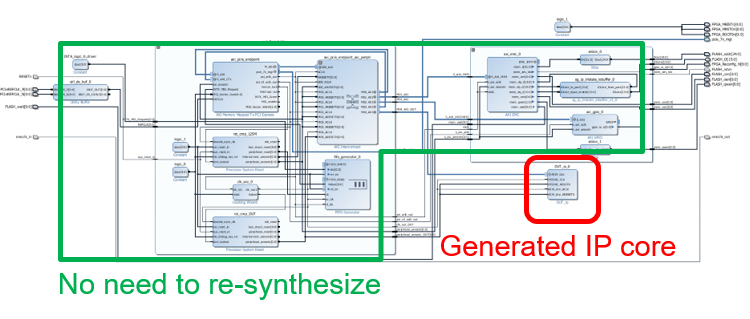

For target platforms that support the IP Core Generation workflow with Xilinx® Vivado®, you can use IP caching. IP caching reduces the synthesis time of reference designs that have many IP modules or that have IP modules with a significant synthesis run time. When you enable IP caching, the Vivado project uses an out-of-context (OOC) workflow. This workflow synthesizes the IP in the reference design out of context from the top-level design. The OOC workflow accelerates project runs because the synthesis tool reuses the IP cache, and does not have to resynthesize the IP when you run the workflow.

If you do not enable IP caching, by default, the Vivado project uses the global synthesis flow. This flow synthesizes the IP modules in the reference design along with the top-level design. In subsequent project runs, this workflow resynthesizes the IP modules in the reference design.

Requirements for Using IP Caching

- Target workflow:

IP Core GenerationSimulink Real-Time FPGA I/Ofor Speedgoat boards that use Xilinx Vivado

- Synthesis tool: Xilinx Vivado

What Is an IP Cache?

An IP cache is a folder that consists of subfolders corresponding to IP modules in the reference design. Each subfolder is organized by a hash index that corresponds to the file name. For each IP module, the subfolder consists of Xilinx Core Instance (XCI) files, Design Checkpoint (DCP) files, and synthesis log files. The DCP is a container file that contains synthesized netlists, black box HDL stub files, and the output clock constraints.

To reuse the IP cache when you run the workflow, the IP synthesis has to match the hash index in the IP cache. The hash index match corresponds to a hit in the IP cache. To hit the IP cache in subsequent runs, use the same:

- Part, language, and target platform settings

- Reference design version

- Target frequency

hdl_prjfolder when you created the IP cache

How IP Caching Works

When you enable IP caching, the Xilinx Vivado project uses an out-of-context (OOC) workflow. The OOC design flow is a bottom-up workflow that:

- Synthesizes the IP modules in the reference design separately from the top-level design. The synthesis output is the Design Checkpoint (DCP) file.

- Synthesizes your top-level design while treating the IP in the reference design as a black box by using the HDL stub files provided with the DCP.

- Implements your design on the target device by linking the netlists from the IP design checkpoint files with your top-level netlist.

For large reference designs, the OOC flow improves synthesis run time, because you do not have to resynthesize the IP when you modify your design and run the workflow. To learn more about the OOC workflow and IP synthesis options, refer to the Xilinx documentation.

Enable IP Caching

Before you enable IP caching, specify IP Core Generation as the target workflow, and then specify the target platform settings. To enable IP caching:

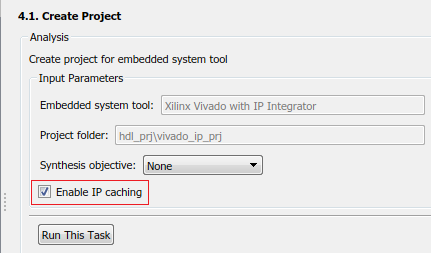

- From the HDL Workflow Advisor, in the Create Project task, select the Enable IP caching check box.

- From the command line, use the

EnableIPCachingproperty of thehdlcoder.WorkflowConfigclass. To use this property, create an object of thehdlcoder.WorkflowConfigclass, or export the HDL Workflow Advisor settings to a script.

hWC = hdlcoder.WorkflowConfig('SynthesisTool','Xilinx Vivado','TargetWorkflow','IP Core Generation');

% ...

% ...

hWC.EnableIPCaching = true;

IP Caching in HDL Coder Reference Designs

Use IP caching for large reference designs that have a significant synthesis time. For example, the HDL Coder™ reference design Default video system (requires HDMI FMC module) is a potential candidate for IP caching.

Note

The Speedgoat IO333-325K board that you use with the Simulink Real-Time FPGA I/O workflow comes with an IP cache. The first time that you run the workflow, the code generator reuses this IP cache, which improves reference design synthesis time.

To enable IP caching, in the HDL Workflow Advisor, specify IP Core Generation as the target workflow, and then specify the target platform settings. Before you run the workflow for the first time:

- In the Create Project task, select the Enable IP caching check box.

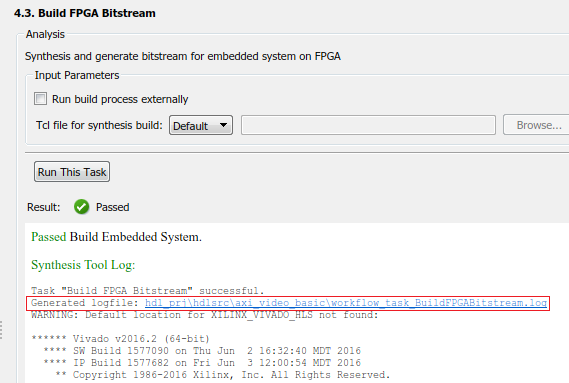

When you run this task, the workflow creates an empty IP cache folder. You can see theipcachefolder in thehdl_prj/vivado_ip_prjpath. - Run the Build FPGA Bitstream task.

This task populates the IP cache folder with synthesis logs and design checkpoint files generated for the HDL IP core and other IP blocks in the reference design. When this task has run successfully, you can see the generated files in theipcachefolder.

When you run the IP Core Generation workflow a second time, in the Build FPGA Bitstream task, you can see an improvement in the task run time. Make sure that you use the same IP settings and hdl_prj folder as the first time that you ran the workflow. When this task has run successfully, to see if your workflow reused the IP cache, open the workflow_task_buildFPGABitstream.log file.

This code snippet shows that the Vivado project launches a maximum number of jobs to synthesize the design and reuse the IP modules in the IP cache folder. You can see that thecacheID of the IP modules match the file names of the subfolders in the ipcache folder.

...

reset_run impl_1

reset_run synth_1

launch_runs -jobs 4 synth_1

... ... ... INFO: [IP_Flow 19-4760] Using cached IP synthesis design for IP system_top_RGBtoYCbCr_0_0, cacheID = 3575924730488800 INFO: [IP_Flow 19-4760] Using cached IP synthesis design for IP system_top_YCbCrtoRGB_0_0, cacheID = e71459f41e26e141 INFO: [IP_Flow 19-4760] Using cached IP synthesis design for IP system_top_xbar_0, cacheID = d0f0971cb77bcaed INFO: [IP_Flow 19-4760] Using cached IP synthesis design for IP system_top_axis2hdmi_0_0, cacheID = 7601a322f9fd0ec4 ...

IP Caching in Custom Reference Designs

If you are using your own custom reference design, IP caching can accelerate reference design synthesis when you run the workflow for the first time. To reuse the IP cache, create an IP cache zip file, and then make sure that the reference design definition file points to this zip file.

To create an IP cache zip file:

- Open the HDL Workflow Advisor for any Simulink® model that has a DUT subsystem, and then run theIP Core Generation workflow to theGenerate RTL Code and IP Core task.

- In the Create Project task, select the Enable IP caching check box, and then click Run This Task. This task creates an empty IP cache folder.

- Run the workflow to the Build FPGA Bitstream task. This task populates the IP cache with the HDL IP core and the reference design IP modules.

- In the IP cache folder, delete the IP core files generated for the DUT. Extract the remaining files from this folder into a zip file, name it

ipcache.zip, and then save the file in the reference design folder.

To reuse the IP cache, in the reference design definition file plugin_rd.m, use the IPCacheZipFile property of the hdlcoder.ReferenceDesign class. By using that property, you add the ipcache.zip file to the Xilinx Vivado project.

function hRD = plugin_rd() % Reference design definition

hRD = hdlcoder.ReferenceDesign('SynthesisTool', 'Xilinx Vivado'); % ... % ... hRD.IPCacheZipFile = 'ipcache.zip';

When you use the workflow to target your custom reference design, the code generator selects the Enable IP caching check box. To see the improvement in synthesis time, run the Build FPGA Bitstream task.

See Also

hdlcoder.Board | hdlcoder.ReferenceDesign