Reconfigurable hardware for neural networks: binary versus stochastic (original) (raw)

Abstract

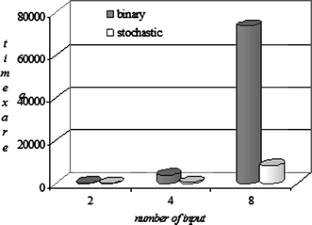

This paper is focused on hardware implementation of neural networks. We propose a reconfigurable, low-cost and readily available hardware architecture for an artificial neuron. For this purpose, we use field-programmable gate arrays i.e. FPGAs. As the state-of-the-art FPGAs still lack the gate density necessary to the implementation of large neural networks of thousands of neurons, we use a stochastic process to implement efficiently the computation performed by a neuron. This paper describes and compares the characteristics of two architectures designed to implement feed-forward fully connected artificial neural networks: the first FPGA prototype is based on traditional adders and multipliers of binary inputs while the second takes advantage of stochastic representation of the inputs. The paper compares both prototypes using the time × area classic factor.

Access this article

Subscribe and save

- Starting from 10 chapters or articles per month

- Access and download chapters and articles from more than 300k books and 2,500 journals

- Cancel anytime View plans

Buy Now

Price excludes VAT (USA)

Tax calculation will be finalised during checkout.

Instant access to the full article PDF.

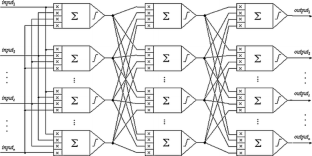

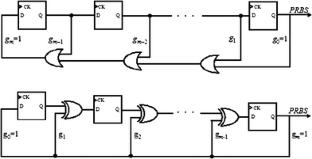

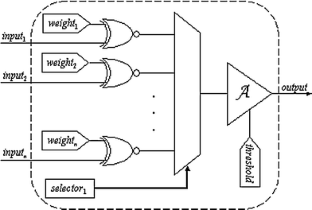

Fig. 1

The alternative text for this image may have been generated using AI.

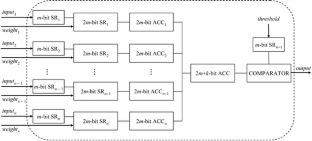

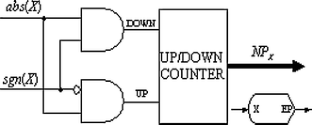

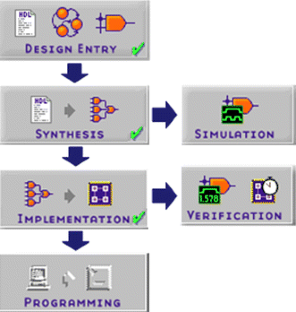

Fig. 2

The alternative text for this image may have been generated using AI.

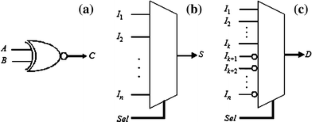

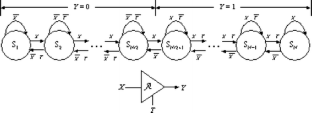

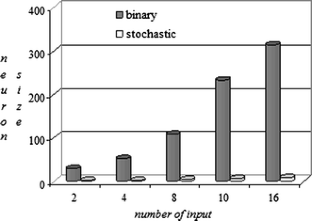

Fig. 3

The alternative text for this image may have been generated using AI.

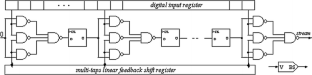

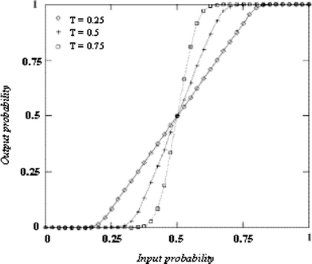

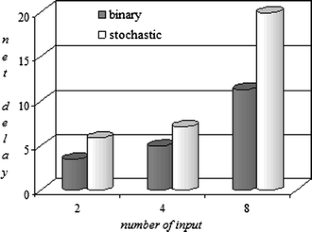

Fig. 4

The alternative text for this image may have been generated using AI.

Fig. 5

The alternative text for this image may have been generated using AI.

Fig. 6

The alternative text for this image may have been generated using AI.

Fig. 7

The alternative text for this image may have been generated using AI.

Fig. 8

The alternative text for this image may have been generated using AI.

Fig. 9

The alternative text for this image may have been generated using AI.

Fig. 10

The alternative text for this image may have been generated using AI.

Fig. 11

The alternative text for this image may have been generated using AI.

Fig. 12

The alternative text for this image may have been generated using AI.

Fig. 13

The alternative text for this image may have been generated using AI.

Similar content being viewed by others

References

- Bade SL, Hutchings BL (1994) _FPGA_-based stochastic neural networks—implementation, IEEE workshop on FPGAs for custom computing machines, Napa

- Brown BD, Card HC (2001) Stochastic neural computation I: computational elements. IEEE Trans Comp 50(9):891–905

Article Google Scholar - Brown BD, Card HC (2001), Stochastic neural computation II: soft competitive learning. IEEE Trans Comp 50(9):906–920

Article Google Scholar - Daalen MV, Jeavons P, Shawe-Taylor J (1993) A stochastic neural architecture that exploits dynamically reconfigurable FPGAs. In: Proceedings of the IEEE workshop on FPGAs for custom computing machines

- Daalen MV, Jeavons P, Shawe-Taylor J (1993) A device for generating binary sequence for stochastic computing. Electron Lett 29(1):80–81

Article Google Scholar - Gaines BR (1969) Stochastic computing systems. Adv Inf Syst Sci 2:37–172

Google Scholar - Hassoun MH (1995) Fundamentals of artificial neural networks. MIT Press, Cambridge

MATH Google Scholar - Moerland P, Fiesler E (1996) Neural network adaptation to hardware implementations. In: Fiesler E, Beale R (eds) Handbook of neural computation

- Navabi Z (1998) VHDL-Analysis and modelling of digital systems, 2nd edn. McGraw Hill

- Xilinx Inc., http://www.xilinx.com

Acknowledgment

We are grateful to the reviewers and the editor that contributed to the great improvement of the original version of this paper with their valuable comments and suggestions. We also are thankful to FAPERJ (Fundação de Amparo à Pesquisa do Estado do Rio de janeiro, http://www.faperj.br) and CNPq (Conselho Nacional de Desenvolvimento Científico e Tecnológico, http://www.cnpq.br) for their continuous financial support.

Author information

Authors and Affiliations

- Department of Electronics Engineering and Telecommunications, Faculty of Engineering, State University of Rio de Janeiro, Rio de Janeiro, Brazil

Nadia Nedjah - Department of Systems Engineering and Computation, Faculty of Engineering, State University of Rio de Janeiro, Rio de Janeiro, Brazil

Luiza de Macedo Mourelle

Authors

- Nadia Nedjah

- Luiza de Macedo Mourelle

Corresponding author

Correspondence toNadia Nedjah.

Rights and permissions

About this article

Cite this article

Nedjah, N., de Macedo Mourelle, L. Reconfigurable hardware for neural networks: binary versus stochastic.Neural Comput & Applic 16, 249–255 (2007). https://doi.org/10.1007/s00521-007-0086-x

- Received: 01 December 2006

- Accepted: 21 December 2006

- Published: 13 March 2007

- Issue date: May 2007

- DOI: https://doi.org/10.1007/s00521-007-0086-x