Когерентность кэша | это... Что такое Когерентность кэша? (original) (raw)

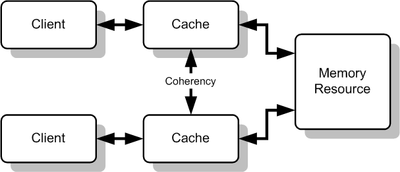

Несколько кэшей для разделяемого ресурса памяти

Когерентность кэша (англ. cache coherence) — свойство кэшей, означающее целостность данных, хранящихся в локальных кэшах для разделяемого ресурса. Когерентность кэшей — частный случай когерентности памяти (en:memory coherence).

Когда клиенты в системе используют кэширование общих ресурсов, например, памяти, могут возникнуть проблемы с противоречивостью данных. Это особенно справедливо в отношении процессоров в многопроцессорной системе. На рисунке «Несколько кэшей для разделяемого ресурса памяти», если клиент в верхней части имеет копию блока памяти из предыдущего чтения, а нижний клиент изменяет блок памяти, копия данных в кэше верхнего клиента становится устаревшей, если не используются какие-либо уведомления об изменении или проверки изменений. Когерентность кэша предназначена для управления такими конфликтами и поддержания соответствия между разными кэшами.

Содержание

- 1 Определение

- 2 Механизмы когерентности кэшей

- 3 Протоколы поддержки когерентности

- 4 Литература

- 5 Примечания

- 6 См. также

Определение

Когерентность определяет поведение чтений и записей в одно и то же место памяти. Кэш называется когерентным, если выполняются следующие условия:

- Если процессор Р записывает значение в переменную Х, то при следующем считывании Х он должен получить ранее записанное значение, если между записью и чтением Х другой процессор не производил запись в Х. Это условие связано с сохранением порядка выполнения программы, это должно выполняться и для однопоточной архитектуры.

- Операция чтения Х процессором

, следующая после того, как другой процессор

, следующая после того, как другой процессор  осуществил запись в Х, должна вернуть записанное значение, если другие процессоры не изменяли Х между двумя операциями. Это условие определяет понятие когерентной видимости памяти.

осуществил запись в Х, должна вернуть записанное значение, если другие процессоры не изменяли Х между двумя операциями. Это условие определяет понятие когерентной видимости памяти. - Записи в одну и ту же ячейку памяти должны быть последовательными. Другими словами, если два процессора записывают в переменную Х два значения: А, затем В — не должно случиться так, чтобы при считывании процессор сначала получал значение В, а затем А.

В этих условиях предполагается, что операции чтения и записи происходят мгновенно. Однако этого не происходит на практике из-за задержек памяти и других особенностей архитектуры. Изменения, сделанные процессором  , могут быть не видны процессору

, могут быть не видны процессору  , если чтение произошло через очень маленький промежуток времени после записи. Модель консистентности памяти определяет, когда записанное значение будет видно при чтении из другого потока.

, если чтение произошло через очень маленький промежуток времени после записи. Модель консистентности памяти определяет, когда записанное значение будет видно при чтении из другого потока.

Механизмы когерентности кэшей

- Когерентность с использованием справочника (directory). Информация о состоянии блока физической памяти содержится только в одном месте, называемом справочником (физически справочник может быть распределен по узлам системы).

- Когерентность с использованием отслеживания (snooping). Каждый кэш, который содержит копию данных некоторого блока физической памяти, имеет также соответствующую копию служебной информации о его состоянии. Централизованная система записей отсутствует. Обычно кэши расположены на общей (разделяемой) шине и контроллеры всех кэшей наблюдают за шиной (просматривают ее) для определения того, не содержат ли они копию соответствующего блока.

- Перехват (snarfing). Когда из какого-либо одного кэша данные переписываются в оперативную память, контроллеры остальных получают сигнал об этом изменении ("перехватывают" информацию об изменении данных) и, если необходимо, изменяют соответствующие данные в своих кэшах.

Системы распределенной разделяемой памяти en:Distributed shared memory используют похожие механизмы для поддержания корректности между блоками памяти в слабосвязанных системах.

Протоколы поддержки когерентности

Протоколы поддержки когерентности отвечают за поддержание корректности данных между всеми кэшами в системе с en:distributed shared memory. Протокол поддерживает когерентность памяти согласно выбранной модели (en:consistency model). Большинство аппаратных протоколов в микропроцессорах соответствуют модели en:sequential consistency, а программные протоколы в системах software distributed shared memory чаще соответствуют моделям en:release consistency или en:weak consistency.

Модели и протоколы поддержки когерентности кэшей:

- Протокол MSI

- Протокол MESI (intel pentium, Core)

- Протокол MOSI

- Протокол MOESI (amd opteron[1])

- MOWESI[2]

- Протокол MERSI

- Протокол MESIF (intel nehalem[1])

- Протокол Write-once

- en:Synapse protocol

- en:Berkeley protocol

- en:Illinois protocol

- en:Firefly protocol (DEC)

- en:Dragon protocol (Xerox)

Литература

- Handy, Jim. The Cache Memory Book. Academic Press, Inc., 1998. ISBN 0-12-322980-4

Примечания

- ↑ 1 2 [1] Multi Processors, their Memory organizations and Implementations by Intel & AMD

- ↑ Принципы работы кэш-памяти — Индикаторы состояния строки