Floating point tolerance check - Specify the floating-point tolerance check option - MATLAB (original) (raw)

Main Content

Specify the floating-point tolerance check option

Since R2024a

Model Configuration Pane: Test Bench

Description

When you generate HLS code from your MATLAB® algorithm containing floating-point types, specify the floating-point tolerance strategy option.

Dependencies

Generate test bench enables this parameter. Enable this parameter by clicking Generate Test Bench in theVerification > Verify with HLS Test Bench >Output Settings pane of the HDL Workflow Advisor.

Settings

Relative Error (default) | ULP Error

Relative Error

This is the default option. When you verify the generated code by using HDL Testbench, HDL Coder™ checks for the floating-point tolerance based on the relative error.

ULP Error

When you verify the generated code by using HLS Testbench, HDL Coder checks for the floating-point tolerance of the native floating-point library or the floating-point target library that your design mapped to based on the ULP error.

Examples

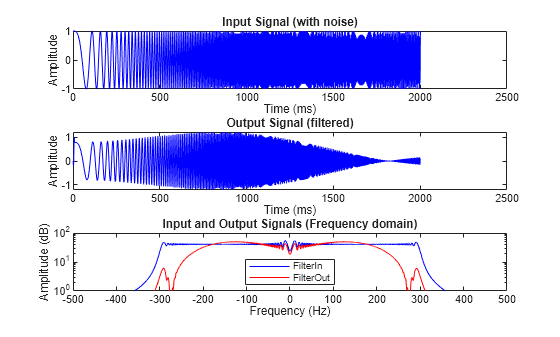

For example, this MATLAB® code configures the HDL configuration object for High Level Synthesis and uses mlhdlc_sfir_tb as the test bench to verify the generated code. It also specifies the FPToleranceStrategy as ULP Error and sets the FPToleranceValue to 1.

% Create HDLConfig object and set the workflow as "High Level Synthesis" cfg = coder.config("hdl"); cfg.Workflow = "High Level Synthesis";

% Test bench options cfg.TestBenchName = "mlhdlc_sfir_tb"; cfg.GenerateHDLTestBench = true;

% Specify the FPToleranceStrategy as "ULP Error" cfg.FPToleranceStrategy = "ULP Error";

% Specify the FPToleranceValue as an integer for "ULP Error" strategy cfg.FPToleranceValue = 1;

codegen -config cfg mlhdlc_sfir -report

Begin MATLAB to HLS Code Generation...

Working on DUT: mlhdlc_sfir.

Using TestBench: mlhdlc_sfir_tb.

Begin HLS Code Generation

Generating Resource Utilization Report resource_report.html.

Working on mlhdlc_sfirClass.hpp as mlhdlc_sfirClass.hpp.

Working on mlhdlc_sfirModule.hpp as mlhdlc_sfirModule.hpp.

To rerun codegen evaluate the following commands...

cgi = load('/tmp/Bdoc25a_2864802_2731108/tp7486429d/hdlcoder-ex34814788/codegen/mlhdlc_sfir/hdlsrc/codegen_info.mat'); inVals = cgi.CodeGenInfo.inVals; cfg = cgi.CodeGenInfo.codegenSettings; codegen -config cfg -args inVals -report

Begin TestBench generation.

Code generation successful.

Collecting data...

Begin HLS test bench file generation with logged samples

Generating test bench data file: x_in.dat.

Generating test bench data file: y_out_expected.dat.

Generating test bench data file: delayed_xout_expected.dat.

Generating test bench file: mlhdlc_sfirClass_tb.hpp

Generating test bench module file: mlhdlc_sfirModule_tb.hpp

Generating HLS Conformance Report mlhdlc_sfir_hdl_conformance_report.html.

HLS Conformance check complete with 0 errors, 0 warnings, and 0 messages.

Code generation successful: View report

Recommended Settings

No recommendations.

Programmatic Use

| Parameter: FPToleranceStrategy |

|---|

| Type: character vector |

| Value: "Relative Error" | "ULP Error" |

| Default: "Relative Error" |

Version History

Introduced in R2024a