Control the Scope of Delay Balancing - MATLAB & Simulink (original) (raw)

This example shows how to balance delays in specific parts of a design, without balancing delays on the entire design.

You can programmatically balance delays by using the BalanceDelays HDL input and output port block property to balance the additional delays introduced by HDL Coder™. You can enable or disable this property on individual input and output ports in your model. For example, in a design containing a data path and a control path, delay balancing can be applied exclusively to the data path of the design. This means focusing on the paths that necessitate data synchronization. You can use BalanceDelays at the design under test (DUT) port level to control how and where HDL Coder balances delays. hdlcoder_localdelaybalancing.slx shows how to disable delay balancing on user-defined stable control paths.

Constrain Delay Balancing to the Data Path

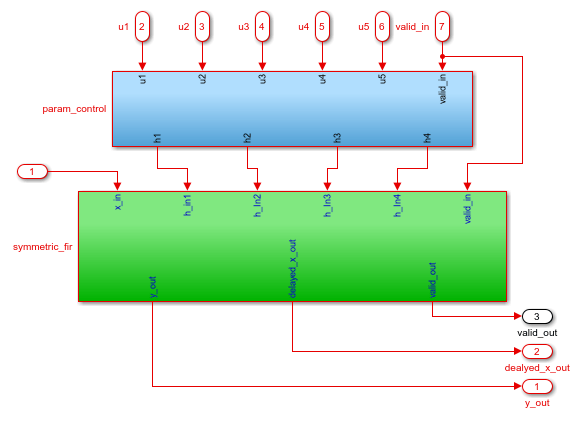

The example model hdlcoder_localdelaybalancing.slx has two subsystems under the device under test (DUT) subsystem, hdlcoder_localdelaybalancing/Subsystem, param_control and symmetric_fir, which contain the control logic and the data path, respectively.

open_system('hdlcoder_localdelaybalancing'); open_system('hdlcoder_localdelaybalancing/Subsystem');

To optimize timing results, each subsystem has one block that has one output pipeline register.

hdldispblkparams('hdlcoder_localdelaybalancing/Subsystem/param_control/And'); hdldispblkparams('hdlcoder_localdelaybalancing/Subsystem/symmetric_fir/Add');

%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%% HDL Block Parameters ('hdlcoder_localdelaybalancing/Subsystem/param_control/And') %%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%

Implementation

Architecture : defaultImplementation Parameters

OutputPipeline : 1%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%% HDL Block Parameters ('hdlcoder_localdelaybalancing/Subsystem/symmetric_fir/Add') %%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%

Implementation

Architecture : LinearImplementation Parameters

OutputPipeline : 1Enable the generation of the validation model and generate HDL code using the makehdl function.

hdlset_param('hdlcoder_localdelaybalancing', 'GenerateValidationModel', 'on'); makehdl('hdlcoder_localdelaybalancing/Subsystem');

Working on the model hdlcoder_localdelaybalancing

Generating HDL for hdlcoder_localdelaybalancing/Subsystem

Using the config set for model hdlcoder_localdelaybalancing for HDL code generation parameters.

Running HDL checks on the model 'hdlcoder_localdelaybalancing'.

Begin compilation of the model 'hdlcoder_localdelaybalancing'...

Working on the model 'hdlcoder_localdelaybalancing'...

The code generation and optimization options you have chosen have introduced additional pipeline delays.

The delay balancing feature has automatically inserted matching delays for compensation.

The DUT requires an initial pipeline setup latency. Each output port experiences these additional delays.

Output port 1: 1 cycles.

Output port 2: 1 cycles.

Output port 3: 1 cycles.

Working on... GenerateModel

Begin model generation 'gm_hdlcoder_localdelaybalancing'...

Rendering DUT with optimization related changes (IO, Area, Pipelining)...

Model generation complete.

Generated model saved at hdlsrc/hdlcoder_localdelaybalancing/gm_hdlcoder_localdelaybalancing.slx

Generating new validation model: 'gm_hdlcoder_localdelaybalancing_vnl'.

Validation model generation complete.

Begin VHDL Code Generation for 'hdlcoder_localdelaybalancing'.

Working on hdlcoder_localdelaybalancing/Subsystem/param_control/params as hdlsrc/hdlcoder_localdelaybalancing/params.vhd.

Working on hdlcoder_localdelaybalancing/Subsystem/param_control as hdlsrc/hdlcoder_localdelaybalancing/param_control.vhd.

Working on hdlcoder_localdelaybalancing/Subsystem/symmetric_fir as hdlsrc/hdlcoder_localdelaybalancing/symmetric_fir.vhd.

Working on hdlcoder_localdelaybalancing/Subsystem as hdlsrc/hdlcoder_localdelaybalancing/Subsystem.vhd.

Code Generation for 'hdlcoder_localdelaybalancing' completed.

Generating HTML files for code generation report at hdlcoder_localdelaybalancing_codegen_rpt.html

Creating HDL Code Generation Check Report file:///tmp/Bdoc24b_2855429_843863/tpb803162c/hdlcoder-ex13756842/hdlsrc/hdlcoder_localdelaybalancing/Subsystem_report.html

HDL check for 'hdlcoder_localdelaybalancing' complete with 0 errors, 0 warnings, and 0 messages.

HDL code generation complete.

Load and update the validation model, rearrange the generated model layout, and open the validation model to the param_control subsystem.

load_system('gm_hdlcoder_localdelaybalancing_vnl'); set_param('gm_hdlcoder_localdelaybalancing_vnl', 'SimulationCommand', 'update'); arrangeLayout('gm_hdlcoder_localdelaybalancing_vnl/Subsystem/param_control') open_system('gm_hdlcoder_localdelaybalancing_vnl/Subsystem/param_control');

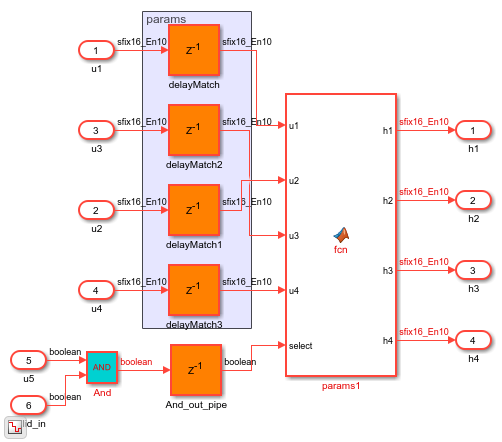

Delay balancing is enabled globally by default and inserts matching delays on both the control path and the data path, as shown in the validation model. For more information on the validation model, see Generated Model and Validation Model.

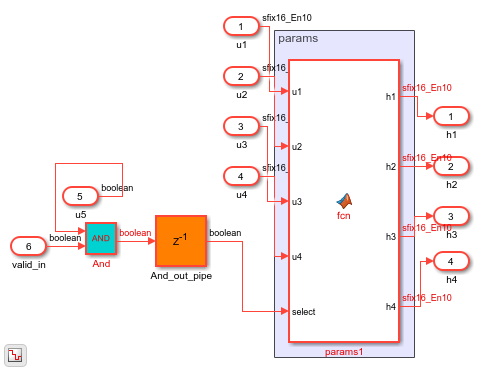

In this example, only the data path, symmetric_fir, requires data synchronization. The inputs u1 through u4 to the param_control subsystem are constant inputs that are coefficients to the FIR filter. The input paths through the DUT subsystem for these coefficients are stable and do not have to synchronize with each other or with the processed data. As a result, you can disable delay balancing for the input ports with constant inputs to the control logic to save on hardware resources. To achieve this, set the HDL block property BalanceDelays for Inport blocks u1 through u4 of the DUT subsystem to off. Because the stable paths propagate through to the lower-level hierarchy in the DUT subsystem, you do not need to disable this property for lower-level Inport blocks inside the param_control or symmetric_fir subsystems.

hdlset_param('hdlcoder_localdelaybalancing/Subsystem/u1', 'BalanceDelays', 'off'); hdlset_param('hdlcoder_localdelaybalancing/Subsystem/u2', 'BalanceDelays', 'off'); hdlset_param('hdlcoder_localdelaybalancing/Subsystem/u3', 'BalanceDelays', 'off'); hdlset_param('hdlcoder_localdelaybalancing/Subsystem/u4', 'BalanceDelays', 'off');

Close the validation model, generate HDL code using the makehdl function, and open the new validation model to the param_control subsystem.

bdclose('gm_hdlcoder_localdelaybalancing_vnl'); hdlset_param('hdlcoder_localdelaybalancing', 'ValidationModelNameSuffix', '_vnl_DBoff') makehdl('hdlcoder_localdelaybalancing/Subsystem'); load_system('gm_hdlcoder_localdelaybalancing_vnl_DBoff'); set_param('gm_hdlcoder_localdelaybalancing_vnl_DBoff', 'SimulationCommand', 'update'); Simulink.BlockDiagram.expandSubsystem('gm_hdlcoder_localdelaybalancing_vnl_DBoff/Subsystem/param_control/params'); open_system('gm_hdlcoder_localdelaybalancing_vnl_DBoff/Subsystem/param_control');

Working on the model hdlcoder_localdelaybalancing

Generating HDL for hdlcoder_localdelaybalancing/Subsystem

Using the config set for model hdlcoder_localdelaybalancing for HDL code generation parameters.

Running HDL checks on the model 'hdlcoder_localdelaybalancing'.

Begin compilation of the model 'hdlcoder_localdelaybalancing'...

Working on the model 'hdlcoder_localdelaybalancing'...

The code generation and optimization options you have chosen have introduced additional pipeline delays.

The delay balancing feature has automatically inserted matching delays for compensation.

The DUT requires an initial pipeline setup latency. Each output port experiences these additional delays.

Output port 1: 1 cycles.

Output port 2: 1 cycles.

Output port 3: 1 cycles.

Working on... GenerateModel

Begin model generation 'gm_hdlcoder_localdelaybalancing'...

Rendering DUT with optimization related changes (IO, Area, Pipelining)...

Model generation complete.

Generated model saved at hdlsrc/hdlcoder_localdelaybalancing/gm_hdlcoder_localdelaybalancing.slx

Generating new validation model: 'gm_hdlcoder_localdelaybalancing_vnl_DBoff'.

Validation model generation complete.

Begin VHDL Code Generation for 'hdlcoder_localdelaybalancing'.

Working on hdlcoder_localdelaybalancing/Subsystem/param_control/params as hdlsrc/hdlcoder_localdelaybalancing/params.vhd.

Working on hdlcoder_localdelaybalancing/Subsystem/param_control as hdlsrc/hdlcoder_localdelaybalancing/param_control.vhd.

Working on hdlcoder_localdelaybalancing/Subsystem/symmetric_fir as hdlsrc/hdlcoder_localdelaybalancing/symmetric_fir.vhd.

Working on hdlcoder_localdelaybalancing/Subsystem as hdlsrc/hdlcoder_localdelaybalancing/Subsystem.vhd.

Code Generation for 'hdlcoder_localdelaybalancing' completed.

Generating HTML files for code generation report at hdlcoder_localdelaybalancing_codegen_rpt.html

Creating HDL Code Generation Check Report file:///tmp/Bdoc24b_2855429_843863/tpb803162c/hdlcoder-ex13756842/hdlsrc/hdlcoder_localdelaybalancing/Subsystem_report.html

HDL check for 'hdlcoder_localdelaybalancing' complete with 0 errors, 0 warnings, and 0 messages.

HDL code generation complete.

Now delay balancing is only active in the data path subsystem and the generated model and code do not contain any delays in the control path subsystem.

Related Examples

- Delay Balancing and Validation Model Workflow in HDL Coder

- Use Delay Absorption While Modeling with Latency