Generate HDL for Mealy and Moore Finite State Machines - MATLAB & Simulink (original) (raw)

Main Content

Stateflow® charts support modeling of three types of state machines:

- Classic (default)

- Mealy

- Moore

For HDL code generation, use Mealy or Moore type state machines. Mealy and Moore state machines differ in these ways.

- The output of a Mealy state machine is a function of the current state and inputs.

- The output of a Moore state machine is a function of the current state only.

The principal advantages of using Mealy or Moore charts as an alternative to Classic charts are:

- Moore charts can generate more efficient code than Classic charts.

- At compile time, Mealy and Moore charts are validated for conformance to their formal definitions and semantic rules, and violations are reported.

To learn more about HDL code generation guidelines for charts, see the Chart (Stateflow) block.

Generate HDL Code for Moore Finite State Machine

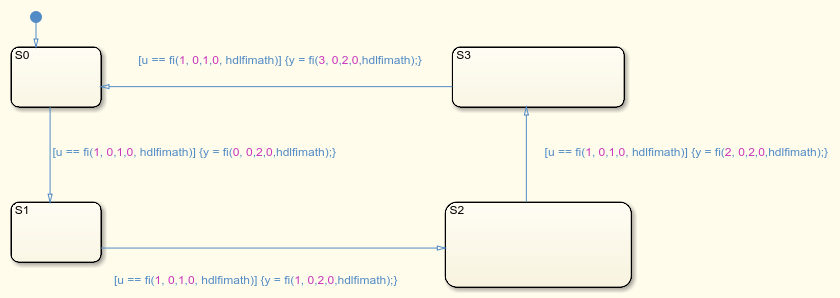

This example shows Stateflow chart of a Moore state machine that uses MATLAB® as the action language.

Open model

Load hdlcoder_fsm_mealy_moore model. The Moore subsystem in hdlcoder_fsm_mealy_moore contains the Stateflow chart Moore_Chart that models a Moore state machine. To open the Moore_Chart, run these commands:

load_system('hdlcoder_fsm_mealy_moore.slx'); open_system('hdlcoder_fsm_mealy_moore/Moore/Moore_Chart');

When generating HDL code for a chart that models a Moore state machine, these conditions apply.

The chart must meet the general code generation requirements as described in the Chart block.

Actions must occur in states only. These actions must be unlabeled. Moore actions must be associated with states, because the output computation is dependent only on states, not input. The configuration of active states at time step

tdetermines the output. If stateSis active when a chart wakes up at timet, then stateScontributes to the output whether or not the state remains active into timet+1.Do not call Simulink® functions. This restriction prevents the output from depending on the input in ways that are difficult for the HDL code generator to verify.

If you disable the Initialize Outputs Every Time Chart Wakes Up parameter, the generated HDL code includes additional registers of the state machine output values.

You can enable clock-driven outputs for a Moore chart by setting the Stateflow chart HDL block property ClockDrivenOutput to

on. For more information, see Guidelines for HDL Code Generation Using Stateflow Charts.

Generate HDL for Mealy Finite State Machine

This example shows Stateflow chart that models a Mealy state machine using MATLAB as the action language. You can also generate the HDL code for Stateflow using HDL Coder™.

Open model

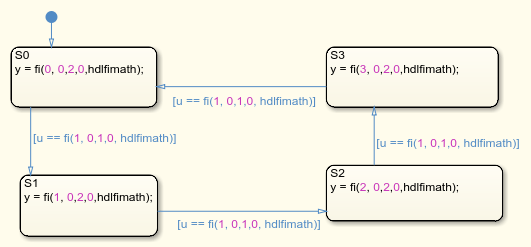

Load hdlcoder_fsm_mealy_moore model. The Mealy subsystem in hdlcoder_fsm_mealy_moore contains the Stateflow chart Mealy_Chart that model a Mealy state machine. To open the Mealy_Chart, run these commands:

load_system('hdlcoder_fsm_mealy_moore.slx'); open_system('hdlcoder_fsm_mealy_moore/Mealy/Mealy_Chart');

When generating HDL code for a chart that models a Mealy state machine, these conditions apply.

The chart must meet the general code generation requirements as described in the Chart block.

Actions must be associated with inner and outer transitions only.

If you disable the Initialize Outputs Every Time Chart Wakes Up parameter, the generated HDL code includes additional registers of the state machine output values.

Mealy actions are associated with transitions. In Mealy machines, the output computation is driven by a change of input values. The dependence of the output on the input is the fundamental distinguishing factor between the formal definitions of Mealy and Moore machines. The requirement that actions result from transitions is to some degree stylistic, rather than required, to enforce Mealy semantics. Because transition conditions are primarily input conditions in any machine type, the output computation ultimately follows input conditions in either type.

Generated HDL Code of the Mealy Chart

This code is the Verilog® code generated for the Mealy chart.

always @(posedge clk or posedge reset) begin : Mealy_Chart_1_process if (reset == 1'b1) begin is_Mealy_Chart <= is_Mealy_Chart_IN_S0; end else begin if (enb) begin is_Mealy_Chart <= is_Mealy_Chart_next; end end end

always @(is_Mealy_Chart, u) begin is_Mealy_Chart_next = is_Mealy_Chart; y_1 = 2'b00; case ( is_Mealy_Chart) is_Mealy_Chart_IN_S0 : begin if (u == 8'sb00000001) begin y_1 = 2'b00; is_Mealy_Chart_next = is_Mealy_Chart_IN_S1; end end is_Mealy_Chart_IN_S1 : begin if (u == 8'sb00000001) begin y_1 = 2'b01; is_Mealy_Chart_next = is_Mealy_Chart_IN_S2; end end is_Mealy_Chart_IN_S2 : begin if (u == 8'sb00000001) begin y_1 = 2'b10; is_Mealy_Chart_next = is_Mealy_Chart_IN_S3; end end default : begin if (u == 8'sb00000001) begin y_1 = 2'b11; is_Mealy_Chart_next = is_Mealy_Chart_IN_S0; end end endcase end

Initialize Outputs Every Time Chart Wakes Up

Mealy and Moore charts have an option to return the output signals to their initial values when the signals are not driven by a state or transition. Select the Initialize Outputs Every Time Chart Wakes Up parameter to enable this behavior. If you clear this parameter, the generated HDL code includes additional registers to store the state machine output values.

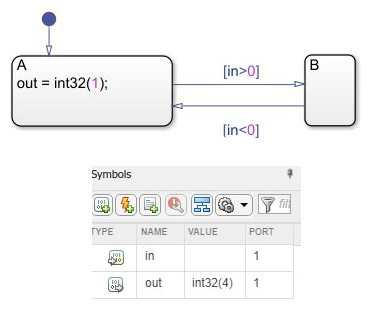

This figure shows a simple Moore chart with two states and one output. The output is set to1 in state A, and the initial value of the output is 4.

When you select the Initialize Outputs Every Time Chart Wakes Up parameter, the output value returns to 4 unless the state machine is in state A. State A sets the output to1. When you clear the Initialize Outputs Every Time Chart Wakes Up parameter, the output value remains at 1 after the machine passes through state A, and does not return to4.

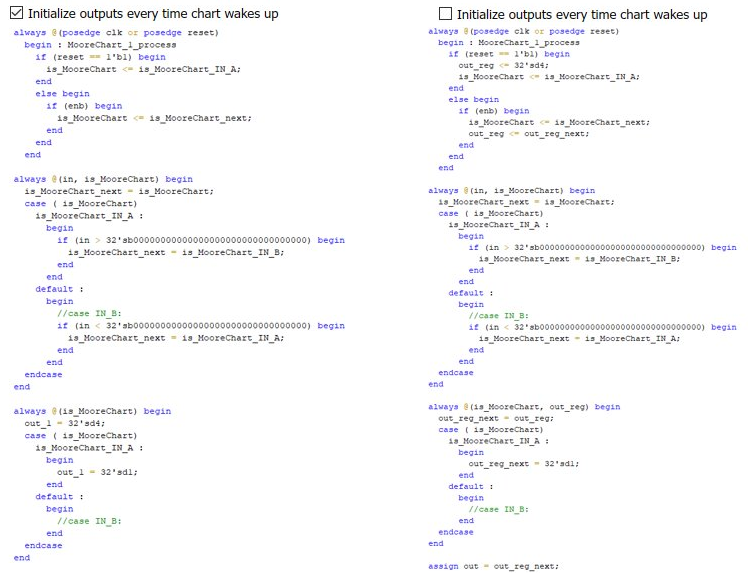

This figure shows the Verilog® code generated for this Moore chart, with Initialize Outputs Every Time Chart Wakes Up selected and then with it cleared.

This table shows the resource usage of these two Moore machines synthesized for a Xilinx® Vivado® Virtex 7 device. When you clear Initialize Outputs Every Time Chart Wakes Up, the generated HDL code includes additional registers for the output state.

| Resource | Initialize Outputs Every Time Chart Wakes UpSelected | Initialize Outputs Every Time Chart Wakes UpCleared |

|---|---|---|

| LUTs | 18 | 20 |

| Registers | 1 | 3 |

| DSPs | 0 | 0 |

| Block RAM | 0 | 0 |

See Also

Chart (Stateflow)