Verify HLS Code That Has an HDL Test Bench - MATLAB & Simulink (original) (raw)

Main Content

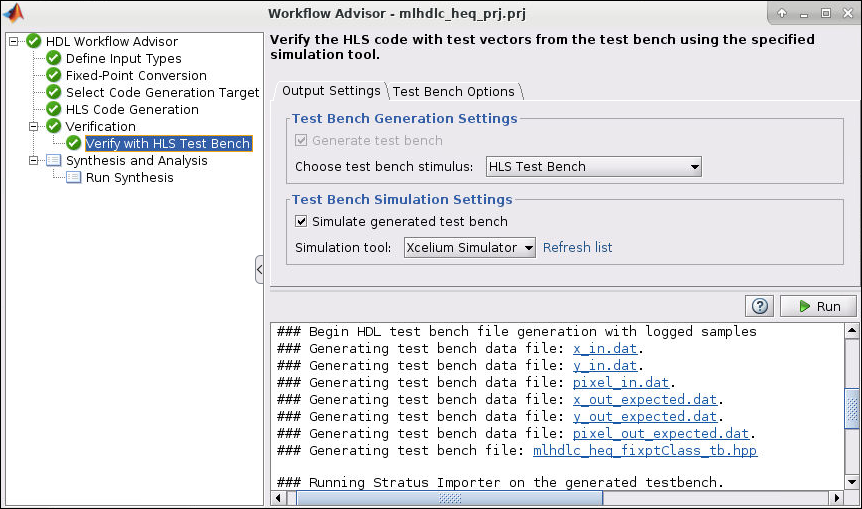

Simulate the generated High-Level Synthesis (HLS) design under test (DUT) with test vectors from the test bench files.

- Start the MATLAB to HDL Workflow Advisor.

- In the HDL Workflow Advisor, select MATLAB to HLS as the Code generation workflow.

- Select the Workflow as High Level Synthesis and Synthesis tool asCadence Stratus HLS in the Select Code Generation Target step.

- For HDL Verification, click Verify with HDL Test Bench.

- Optionally, select Simulate generated HDL test bench. This option enables MATLAB® to simulate the HLS test bench by using the HLS DUT.

- Click Run.

If the test bench and simulation executes without error, you see messages similar to these messages in the message pane:

Begin TestBench generation.

Code generation successful.

Collecting data...

Begin HDL test bench file generation with logged samples

Generating test bench data file: /tmp/mlhdlc_sfir/codegen/mlhdlc_sfir/hdlsrc/x_in.dat.

Generating test bench data file: /tmp/mlhdlc_sfir/codegen/mlhdlc_sfir/hdlsrc/y_out_expected.dat.

Generating test bench data file: /tmp/mlhdlc_sfir/codegen/mlhdlc_sfir/hdlsrc/delayed_xout_expected.dat.

Generating test bench file: mlhdlc_sfir_fixptClass_tb.hpp

Running Stratus Importer on the generated testbench.

Working on mlhdlc_sfir_fixpt_bdw_import_log.txt as /tmp/mlhdlc_sfir/codegen/mlhdlc_sfir/hdlsrc/stratus_prj/mlhdlc_sfir_fixpt_bdw_import_log.txt.

Stratus Importer successful.

Simulating the design 'mlhdlc_sfir_fixpt' using 'Cadence Stratus HLS'.

Generating Simulation Report /tmp/mlhdlc_sfir/codegen/mlhdlc_sfir/hdlsrc/stratus_prj/mlhdlc_sfir_fixpt_sim_BEH_log_sim.txt

Simulation successful.

Elapsed Time: ' 64.6783' sec(s)

If the errors appear in the message pane, fix the errors and clickRun.

Additional Notes

- After clicking Run, the test bench generation starts generating the

.datfiles, such asx_in.datandy_out_expected.dat, that contains the input and the expected output values to the top-level DUT and a test bench class file. - When the test bench files are generated, the Stratus Importer is run by using Cadence Stratus HLS tool. It generates a Stratus HLS project in the current working folder.

- The simulation compiles and executes the generated HLS code and test bench with input values stored in the

x_in.datfile. The simulation can verify the numeric match of the generated HLS code to the MATLAB code by comparing the HLS output with the expected output values stored in they_out_expected.datfile.