Generate HDL Code When Using Vector Data Type Inputs with Enable Signal Port - MATLAB & Simulink (original) (raw)

Main Content

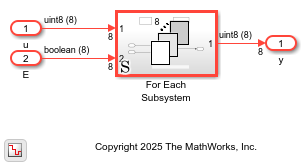

This example shows how to generate HDL code for the Unit Delay Enabled Synchronous block when you connect a signal that uses a vector data type to the enable signal port. Use the For Each Subsystem block, that maps each element in the vector to the enable inputs of the Unit Delay Enabled Synchronous block.

Open the UnitDelayEnabledSynchronousWithVectorEnable model, which includes a DUT subsystem modeled using a For Each Subsystem. This subsystem contains a Unit Delay Enabled Synchronous block. The input port U connects to a constant vector input, the enable signal port E connects to a 1-by-8 vector signal.

Open and Load Model

To load and open the UnitDelayEnabledSynchronousWithVectorEnable model use these commands:

load_system("UnitDelayEnabledSynhronousWithVectorEnable"); set_param("UnitDelayEnabledSynhronousWithVectorEnable",'SimulationCommand','Update') open_system("UnitDelayEnabledSynhronousWithVectorEnable/DUT");

Generate HDL Code

You can generate the HDL code for the DUT subsystem by using the makehdl command:

makehdl("UnitDelayEnabledSynhronousWithVectorEnable/DUT")

The generated HDL code contains this code snippet, which demonstrates how the elements of the vector mapped to the inputs of the Unit Delay Enabled Synchronous blocks.

assign u[0] = u_0; assign u[1] = u_1; assign u[2] = u_2; assign u[3] = u_3; assign u[4] = u_4; assign u[5] = u_5; assign u[6] = u_6; assign u[7] = u_7;

assign E[0] = E_0; assign E[1] = E_1; assign E[2] = E_2; assign E[3] = E_3; assign E[4] = E_4; assign E[5] = E_5; assign E[6] = E_6; assign E[7] = E_7;

generate genvar k; for(k = 0; k < 8; k = k + 1) begin : u_For_Each_Subsystem_gen For_Each_Subsystem u_For_Each_Subsystem (.clk(clk), .reset(reset), .enb(enb), .In1(u[k]), // uint8 .In2(E[k]), .Out1(For_Each_Subsystem_Out1[k]) // uint8 ); end endgenerate