Clocking and Multirate Design - MATLAB & Simulink (original) (raw)

Clock generation, HDL code generation guidelines for multirate models

Generate HDL code for multirate models with single or multiple clocks and clock control elements, such as clock resets and timing controllers.

Topics

- Generate a Global Oversampling Clock

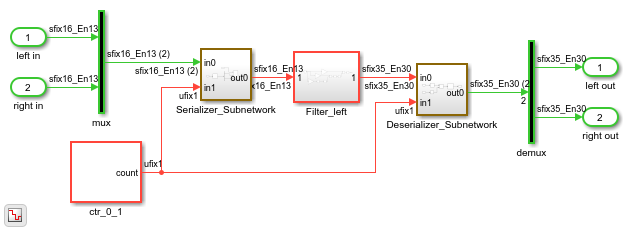

Generate a global oversampling clock to integrate your DUT into a larger design. - Code Generation from Multirate Models

Overview of HDL code generation for single-clock, single-tasking multirate models. - Multirate Model Requirements for HDL Code Generation

Guidelines for setting up multirate models and blocks for HDL code generation. - Timing Controller for Multirate Models

Learn about timing controllers and clock enables in a multirate model. - Generate Reset for Timing Controller

How to generate reset for timing controller. - Using Triggered Subsystems for HDL Code Generation

How to use Triggered Subsystems, Trigger As Clock property, and generate HDL code. - Use Triggered Subsystem for Asynchronous Clock Domain

Design a model for an asynchronous clock domains using triggered subsystems. - Generate Clock Enable Signals

Generation of clock enable signals in your DUT for single rate and multirate models.

Featured Examples

Using Multiple Clocks in HDL Coder

Instantiate multiple top-level synchronous clock input ports in HDL Coder™.

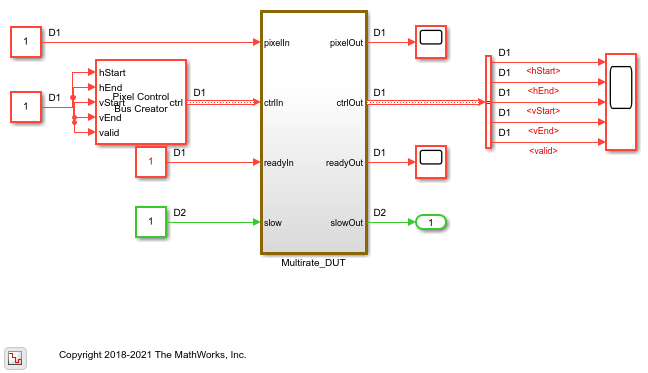

Generate IP Core from Multirate Model

Learn various example designs that use multiple sample rates with IP Core Generation workflow.

HDL Code Generation for a System with Multiple Independent Clock Domains

You can generate HDL code for a system with multiple independent clock domains using HDL Coder™ by:

- Since R2024b

- Open Live Script