Hierarchical Designs and Synchronous Hardware Behavior - MATLAB & Simulink (original) (raw)

Create subsystems and hierarchical HDL designs with State Control block

The HDL Coder block library contains many blocks that you can add to your Simulink® modeling environment and develop your HDL algorithm. To model large designs, you can divide your model into subsystems and create hierarchical designs. For synchronous hardware behavior and to generate hardware-friendly HDL code, use the State Control block inside the subsystems.

To filter the Simulink Library Browser to show only HDL-supported blocks, enterhdllib. The blocks listed in this section include those blocks that are only available in theHDL Coder library. Blocks such as Foreach Subsystem and Atomic Subsystem are available in the Simulink library in the Library Browser.

For a filtered list of Simulink blocks supported for HDL code generation, see Simulink Block List (HDL Code Generation).

Functions

| hdllib | Display blocks that are compatible with HDL code generation |

|---|

Checks

| Check for obsolete Unit Delay Enabled/Resettable Blocks |

|---|

| Check for invalid top level subsystem |

Blocks

| Unit Delay Enabled Synchronous | Delay input signal by one sample period when external Enable signal is true |

|---|---|

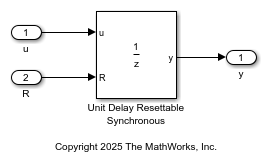

| Unit Delay Resettable Synchronous | Delay input signal by one sample period when external Reset signal is false |

| Unit Delay Enabled Resettable Synchronous | Delay input signal by one sample period when external Enable signal is true and external Reset signal is false |

| Tapped Delay Enabled Synchronous | Delay scalar signal multiple sample periods and output all delayed versions when external Enable signal is true (Since R2023a) |

| Tapped Delay Resettable Synchronous | Delay scalar signal multiple sample periods and output all delayed versions when external Reset signal is false (Since R2023a) |

| Tapped Delay Enabled Resettable Synchronous | Delay scalar signal multiple sample periods and output all delayed versions when external Enable signal is true and external Reset signal is false (Since R2023a) |

| Enabled Delay | Delay input signal by fixed or variable sample periods when external enable signal is true (Since R2024b) |

| Enabled Resettable Delay | Delay input signal by fixed or variable sample periods when external Enable signal is true and external Reset signal is false (Since R2024b) |

| State Control | Specify synchronous reset and enable behavior for blocks with state |

|---|---|

| Synchronous Subsystem | Represent subsystem that has synchronous reset and enable behavior |

| Enabled Synchronous Subsystem | Represent enabled subsystem that has synchronous reset and enable behavior |

| Resettable Synchronous Subsystem | Represent resettable subsystem that has synchronous reset and enable behavior |

Topics

- Synchronous Subsystem Behavior with the State Control Block

Description of a State Control Block and how it generates cleaner HDL code. - Generating HDL Code for Subsystems with Array of Buses

Generate HDL code for subsystems that use array of buses in the design. - Generate Reusable Code for Subsystems

Generate shared code for identical subsystems or subsystems identical except for their mask parameter values. - Generate Parameterized Code for Referenced Models

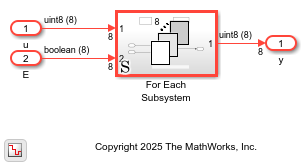

Generate VHDL®generic, Verilog® or SystemVerilogparameterfor model arguments in a model reference. - Generate HDL Code for Blocks Inside For Each Subsystem

An example that shows how to model and generate HDL code for blocks inside a For Each Subsystem. - Model Referencing for HDL Code Generation

Generate HDL code for referenced models. - Generate Incremental HDL Code for Referenced Models

When incremental code is generated for referenced models. - Set Configuration Parameters for HDL Code Generation of Model Hierarchies

Satisfy model reference hierarchy requirements to enable HDL code generation. - Generate HDL Code with Record or Structure Types for Bus Signals

Generate VHDL code with record or structure types for bus signals at different subsystem-level interfaces.

Featured Examples

Using the State Control Block to Generate More Efficient Code with HDL Coder

Use the State Control block to generate hardware-friendly HDL code using HDL Coder™.

Resettable Subsystem Support in HDL Coder

Use Resettable Subsystems in HDL Coder™.

Using ForEach Subsystems in HDL Coder

Use a For Each Subsystem to implement a streaming square root algorithm by cascading identical CORDIC iterations. You can then generate code for the algorithm by using HDL Coder™.

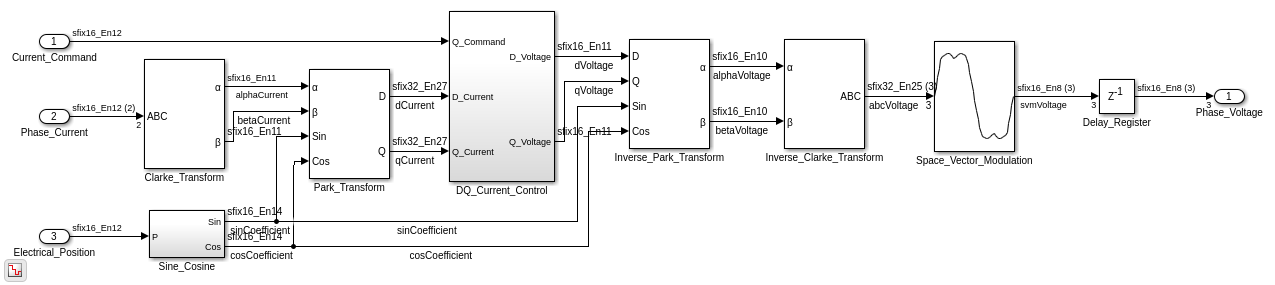

Field-Oriented Control of a Permanent Magnet Synchronous Machine

Generate HDL code for a Field-Oriented Control (FOC) algorithm for a Permanent Magnet Synchronous Machine (PMSM).

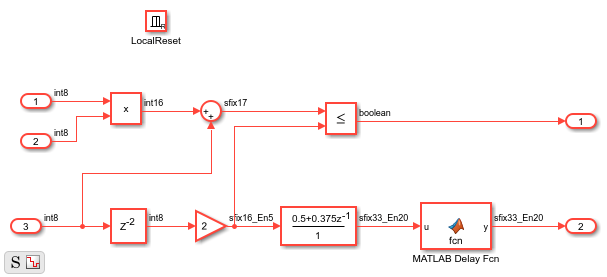

Simulate and Generate HDL Code for Tapped Delay Enabled Resettable Synchronous Block

Implement the Tapped Delay Enabled Resettable Synchronous block in a Simulink® model that a delays scalar signal multiple sample periods and output all delayed versions when external Enable signal is true and external Reset signal is false. You also generate HDL code for the model.

Generate HDL Code When Using Vector Data Type Inputs with Enable Signal Port

Generate HDL code for the Unit Delay Enabled Synchronous block when using vector data inputs with Enable signal port.

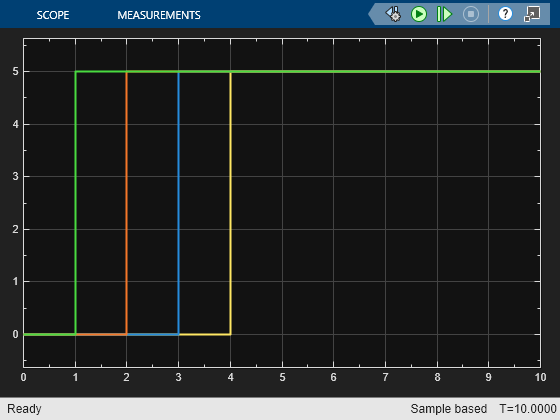

Simulate and Generate HDL Code for Unit Delay Resettable Synchronous Block

Simulate and generate HDL code for the Unit Delay Resettable Synchronous block.